Welcome to the bedrock. Digital Logic Design is where the abstract world of computing becomes physical. It’s the subject that answers the question: “How do ones and zeros actually do anything?” This past paper isn’t just an exam—it’s a blueprint. A blueprint for the very circuits that make every processor, every memory chip, and every digital device think.

If you’ve ever wondered how software commands turn into hardware action, DLD is your decoder. This paper tests your ability to not just understand logic, but to build with it.

What This Paper Builds, Step-by-Step:

1. The Atomic Level: Gates and Boolean Algebra

It starts simple—AND, OR, NOT, XOR. But quickly, you’re not just drawing gates; you’re optimizing them. Questions like “Simplify this expression using K-maps” or “Convert this truth table to a minimal SOP form” are foundational. This is the grammar of digital speech.

2. The Architecture Emerges: Combinational Circuits

This is where logic becomes function. You’ll design:

- Adders & Subtractors (the math heart of the CPU)

- Multiplexers & Decoders (the traffic controllers of data paths)

- Comparators & Encoders (the decision-makers)

You won’t just analyze them—you’ll build them from scratch. The exam often gives a real-world scenario: *”Design a circuit for a 7-segment display driver.”* It’s theory with instant, tangible application.

3. The Introduction of Memory: Sequential Circuits

Here’s the paradigm shift—when circuits learn to remember. Flip-flops (SR, JK, D, T) become the building blocks of:

- Registers (tiny, fast storage)

- Counters (for clocks, timers, control sequences)

- Finite State Machines (FSMs)

The FSM questions are critical. Designing a state diagram and then implementing it with flip-flops and combinational logic is the quintessential DLD problem—it’s where you see how complex behavior (like a vending machine or traffic light controller) emerges from simple, clocked logic.

4. The Bigger Picture: Memory and System Design

Higher-level papers might introduce RAM/ROM basics or simple processor datapaths. It connects DLD to Computer Architecture, showing you the next step in the journey.

The Paper’s Signature Challenge:

Precision. Unlike some subjects where partial understanding can earn partial marks, DLD is often binary in its marking—a single wrong connection in a circuit diagram can break the entire logic. Time management is brutal: K-maps and simplification can eat up minutes if you’re not fluent.

How to Conquer This Paper:

- Practice Like a Musician Scales.

Boolean simplification, K-map filling, and flip-flop excitation tables are muscle memory. Drill them until they’re automatic. - Draw, Draw, Draw.

Get comfortable with neat, clear circuit diagrams. Label everything. A messy diagram leads to logic errors and lost marks. - Think in Layers.

Break every problem down:

Step 1: What’s the required behavior? (Truth table/State diagram)

Step 2: What’s the minimal logic? (Simplify)

Step 3: What components do I use? (Gate types, Flip-flop choice)

Step 4: How do I connect them? (Drawing the circuit) - Verilog/VHDL Alert:

If your syllabus includes HDL, the paper may ask for code snippets alongside traditional design. Treat the HDL question as another way of drawing—it’s the same logic, just a different language.

This past paper is more than a test; it’s a rite of passage. Solving it means you’ve learned to think in gates and clocks, to see the elegant machinery beneath the screen. It’s the first time you truly design, not just program. And that’s a powerful feeling.

Digital logic design (DLD) Mid term Examination 2021

Q.No.1

(A) A hexadecimal odometer displays F5EC.what are the next 7 readings?

(B) A microcomputer has memory locations from 000 to 0FF.each memory location stores 1 bytes. In decimal, how many bites can the microcomputer store in its memory?

(c) Implement y=AB+CD using NOR gates only.

(d) An XOR gate has 6 inputs. How many input words are in its truth table?

(E) Why the gates are called decision making elements? How many inputs signal can a gate have?

(F) What are the fundamental product for each of the input words ABCD=0010,ABCD=1101 AND ABCD=1100.

(G) Why the gates are called decisions making elements? How many input signal can a gate have? How many output signals?

(H) What is meant by universal gate? What is the main difference between inverter and controlled inverter? Show the circuit diagram of a controlled inverter.

(I) Convert (21+your own registration number) into binary, octal and hexadecimal number system. The input is in decimal format.

(J) Reconvert the answer of above part (1) back into decimal.

Q.No.2

Draw the circuit diagram of a decimal to binary encoder.

Q.No.3

Design the circuit diagram of a grey code to binary converter.

Q.No.4

Differentiate between half adder, full adder and binary adder. Implement the circuit diagram of a full adder starting from truth table.

Q.No.5

A truth table has four inputs variables. The first eight outputs are 0’s and the last eight output are 1’s.draw the k-Map and write down the simplified expression

Digital logic design (DLD) paper 2 2020

DLD paper 3 2020

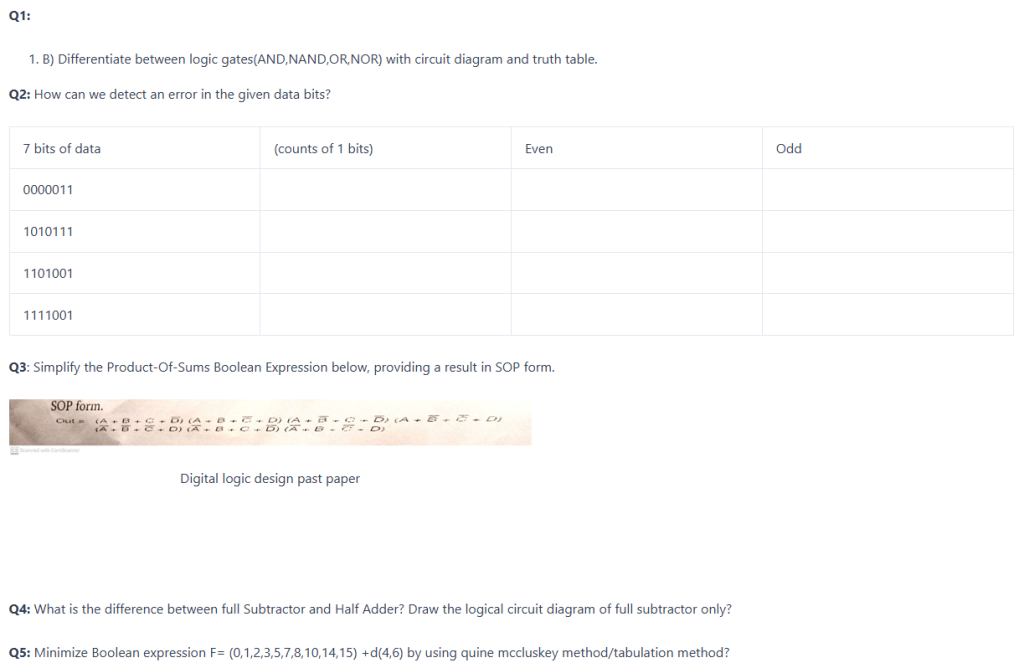

Q1:

- A hexadecimal odometer displays F5EC. What are the next 7 reading?

- A microcomputer has memory locations from 000 to 0FF. Each memory location stores 1 byte. In decimal, how many bites can the microcomputer store in its memory?

- Implement Y= AB + CD using NOR gates only.

- An XOR gate has 6 inputs. How many input words are in its truth table?

- Why the gates are called decision making elements? How many input signals can a gate have?

- What are the fundamental product for each of the input words ABCD = 0010, ABCD = 1101 and ABCD = 1100?

- Why the gates are called decision making elements? How many input signals can a gate have? How many output signals?

- What is meant by universal gate?

What is the main difference between inverter and controller inverter? Show the circuit diagram of a controlled inverter?

- Convert (21+your own registration number) into binary, octal and Hexadecimal number system. The input is in decimal format?

- Reconvert the answers of the above part (1) back into decimal?

Q2: Draw the circuit diagram of the decimal to binary encoder?

Q3: Design the circuit diagram of a grey code to binary converter?

Q4: Differentiate between half adder, full adder and binary adder. Implement the circuit diagram of a full adder starting from truth table?

Q5: A truth table has four input variables. The first eight outputs are 0’s and the last eight output are 1’s. Draw the K-Map and write down the simplified expression?

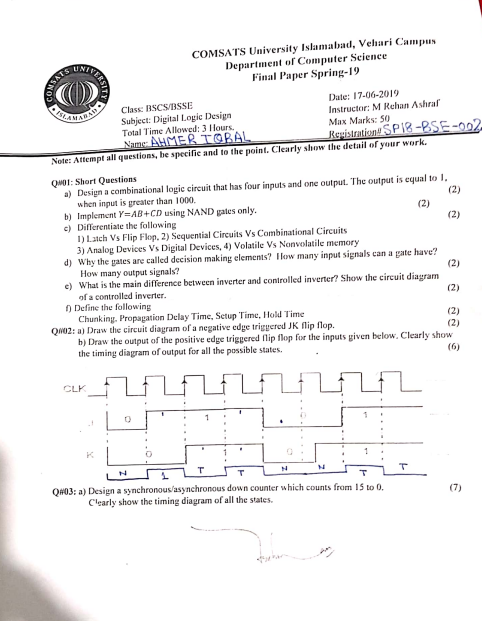

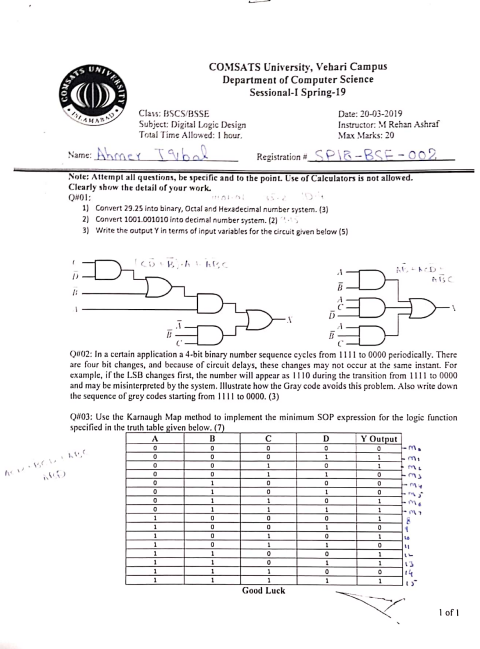

DLD Paper 4 2019

Q1:

a) A hexadecimal odometer displays FSEC. What are the next 7 readings?

b) A microcomputer has memory locations from 00 to OFF. Each memory location stores I byte. In decimal, how many bites can the microcomputer store in its memory”

c) Implement Y – AB + CD using NOR gates only.

d) An XOR gate has 6 inputs. How many input words are in its truth table?

Why the gates are called decision making elements? How many input signals can a gate have?

What are the fundamental product for each of the input words ABCD – 0010, ABCD = 1101 and ABCD

– 1100.

Why the gates are called decision making elements? How many input signals can a gate have? How many

output signals?

What is meant by universal gale?

What as the main difference between inverter and controlled inverter? Show the circuit diagram

or a controlled inverter.

P Convert (21 – your own registration number) into binary, octal and Hexadecimal number system The input 1s in decimal format.

Reconvert the answers of above part (i) back into decimal.

Q2: Draw the circuit diagram of a decimal to binary encoder.

Q3: Design the circuit diagram of a grey code to binary converter.

Q4: Differentiate between half adder, full adder and binary adder. Implement the circuit diagram of a full adder starting from truth table.

Q5: A, truth table has four input variables. The first eight outputs are O’s and the last eight output are Is.

Draw the K-Map and write down the simplified expression.

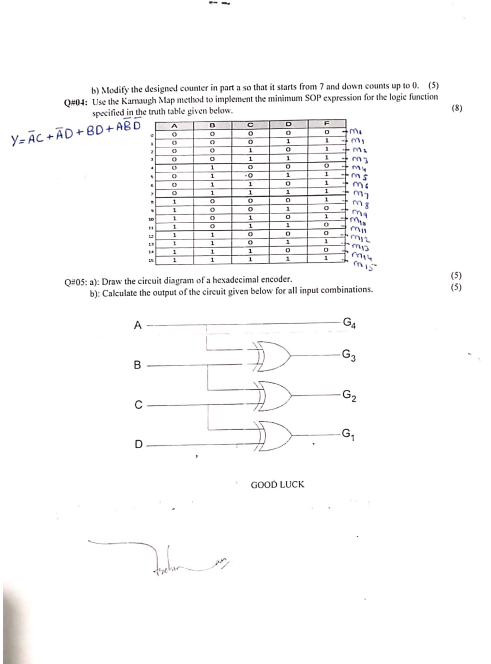

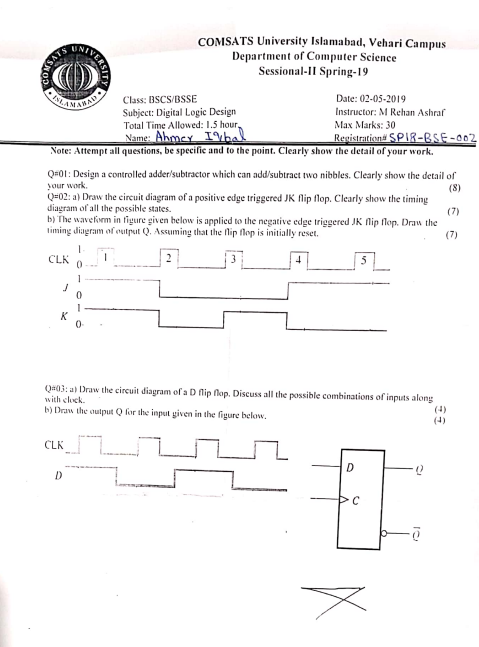

DLD Paper 5 2019

DLD paper 6 2018

DLD paper 7 2018